EnCore Processor

Encyclopedia

University of Edinburgh School of Informatics

The School of Informatics is an academic unit of the University of Edinburgh, in Scotland, responsible for research, teaching, outreach and commercialisation in Informatics....

. The following are key features of the EnCore microprocessor

Microprocessor

A microprocessor incorporates the functions of a computer's central processing unit on a single integrated circuit, or at most a few integrated circuits. It is a multipurpose, programmable device that accepts digital data as input, processes it according to instructions stored in its memory, and...

family:

- 5 stage pipeline

- highest operating frequency in its class

- lowest possible dynamic energy consumption - 99% of flip-flops automatically clock-gatedClock gatingClock gating is a power-saving technique used in many synchronous circuits-Description:Clock gating is a popular technique used in many synchronous circuits for reducing dynamic power dissipation. Clock gating saves power by adding more logic to a circuit to prune the clock tree...

using typical synthesis tools - most non-memory operations achieving single-cycle latency, and no more than one load-delay slot

- easy configurability of cache architectures

- compact baseline instruction set architecture (ISAInstruction setAn instruction set, or instruction set architecture , is the part of the computer architecture related to programming, including the native data types, instructions, registers, addressing modes, memory architecture, interrupt and exception handling, and external I/O...

), including freely-mixed 16-bit and 32-bit encodings for maximum code density - no overhead for switching between 16- and 32-bit instruction encodings

All of the EnCore test chips are named after hills in Edinburgh

Hills in Edinburgh

Edinburgh, the capital of Scotland is traditionally said to have been "built on Seven Hills", presumably in an attempt to liken the city with other cities supposedly built on seven hills such as Rome and Lisbon...

; Calton

Calton Hill, Edinburgh

Calton Hill is a hill in central Edinburgh, Scotland, just to the east of the New Town. Views of, and from, the hill are often used in photographs and paintings of the city....

, being the smallest, is the first of these.

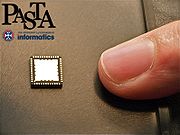

EnCore Calton

CMOS

Complementary metal–oxide–semiconductor is a technology for constructing integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits...

process using a standard ASIC flow.

- 130nm implementation of EnCore processor in baseline configuration extended with barrel shifterBarrel shifterA barrel shifter is a digital circuit that can shift a data word by a specified number of bits in one clock cycle. It can be implemented as a sequence of multiplexers , and in such an implementation the output of one mux is connected to the input of the next mux in a way that depends on the shift...

, multiplier, and a full set of 32 general purpose registersProcessor registerIn computer architecture, a processor register is a small amount of storage available as part of a CPU or other digital processor. Such registers are addressed by mechanisms other than main memory and can be accessed more quickly...

. - Contains bus interface and system control functions, in addition to the processor.

- Implemented with 8KB direct-mapped instruction- and data-cache.

- Complete system-on-chipSystem-on-a-chipA system on a chip or system on chip is an integrated circuit that integrates all components of a computer or other electronic system into a single chip. It may contain digital, analog, mixed-signal, and often radio-frequency functions—all on a single chip substrate...

occupies 1 mm2 of silicon at 75% utilization. - Chip-level power consumption is 25 mW at 250 MHz.

- First silicon samples operate above a frequency of 375 MHz at typical voltage and temperature.

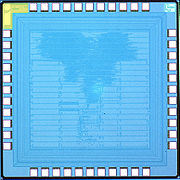

EnCore Castle

The second silicon implementation of an extended EnCore processor is a test-chipcodenamed Castle, fabricated in a generic 90nm CMOS process. All of the EnCore

test chips are named after hills in Edinburgh; Castle is named after the rock on

which Edinburgh Castle is built.

The Castle chip contains an extended version of the EnCore processor, together

with a 32KB 4-way set-associative Instruction Cache, and a 32KB 4-way

set-associative Data Cache. It is embedded within a system-on-chip (SoC) design

that provides a generic 32-bit memory interface, as well as interrupt, clocks

and reset signals.

- 90nm implementation is based on a generic free foundry libraries, and a stack of 9 metal layers.

- Complete design occupies 2.25 sq.mm on a 1.875 x 1.875 mm die. This includes the baseline CPU, the reconfigurable Configurable Flow Accelerator (CFA) extension logic, two 32KB caches, and the off-chip interfaces.

- Designed to operate on a core voltage of 0.9V to 1.1V, with 2.5V LVCMOS I/O signals.

- Packaged in a 68-pin Ceramic LCC.

- First silicon samples operate at 600MHz.

- Chip-level power consumption is 70mW at 600 MHz, under typical conditions.

- Complete design flow, from RTL to GDSII, was performed by the PASTA team. This was based on an in-house developed design flow using Synopsys Design Compiler for topological synthesis, and IC Compiler for automated place-and-route.

- Over 97% of all flip-flops in the design were automatically clock-gated during logic synthesis.

- LVS and DRC checks were performed using Calibre, from Mentor Graphics.